# 1GHz 고효율 Class F 전력 증폭기 개발

이종우, 차정현, 김장헌, 김범만 포항공과대학교 전자전기공학과 tel) 054-279-5584 / fax) 054-279-8115

## **Development of a 1GHz High Efficiency Class F Power Amplifier**

Jongwoo Lee, Jeonghyeon Cha, Jangheon Kim and Bumman Kim Department of Electronic and Electrical Engineering, Pohang University of Science and Technology (POSTECH)

E-mail: simille@postech.ac.kr

### **Abstract**

This paper describes a highly efficient class F power amplifier. The design has been carried out at 1GHz using a LDMOS transistor with a 10 watt of peak envelope power (PEP). For the implementation, the harmonic control network has been realized using transmission lines. Drain efficiency of 79% and power added efficiency (PAE) of 74.8% were measured at an output power of 40.5dBm for continuous wave (CW) signal. The harmonic power has been suppressed below -40dBc.

#### I. 서론

스위치 모드 증폭기는 기본적으로 입력 신호 주기 동안 출력 전압 파형과 출력 전류 파형의 overlap 을 없앰으로써 DC 전력 소모를 최소화하는 방식이 다. 이러한 고효율 증폭기는 냉각 시스템의 비용을 절감할 뿐만 아니라 시스템의 부피와 무게를 줄일 수 있다는 장점을 지닌다.

여러 가지 형태의 고효율 증폭기가 있지만 고주파 에서도 높은 효율을 성취할 수 증폭기는 class E와 class F가 대표적이다[1]. Class E는 스위칭 증폭기 의 대표적인 형태로 회로가 간단하고 소자의 출력 capacitance를 회로적으로 보상하여 스위칭 손실을 제거할 수 있어 비교적 높은 주파수에서도 우수한 성능을 보인다. 그러나 출력 전력이 capacitance에 따라서 변하기 때문에 민감도가 높고 고 전력 증폭 기를 구현하기는 힘들다. 반면 class F는 출력 파형 의 overlap을 없애기 위해, 증폭기가 saturation되 었을 때 harmonic을 제어하는 방식을 채택한다. 이 때 제어되는 harmonic의 수가 많아질수록 효율은 증가하지만 회로가 복잡해지기 때문에, 둘 사이에서 타협이 필요하게 된다. 사실 모든 harmonic을 제어 하는 것이 불가능하기 때문에 class F는 100%의 효율을 달성할 수 없다. 그럼에도 불구하고 class F 는 제한된 수의 harmonic만을 제어하면서도 고주파에서 class E와 비슷한 성능을 보여주고 있다[2]. 또한 class F는 class E에 비해 단위 크기 당 보다높은 출력 전력을 얻을 수 있는 장점도 있다.

본 논문은 1GHz에서 구현된 class F 전력 증폭기의 측정 결과를 제시하며, 최대 출력 전력이 10W인비교적 고출력 소자를 사용하였다.

#### Ⅱ. Class F 전력 증폭기

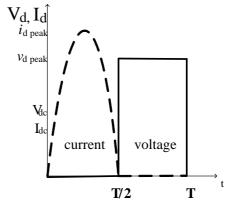

그림 1은 Class F 증폭기의 이상적인 출력 전압 및 전류 파형을 나타낸다. 그림 1에서 보듯이 전압

그림 1. 이상적인 Class F 중폭기 출력 파형

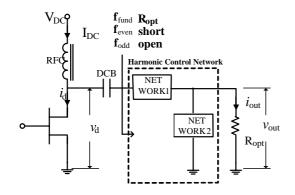

그림 2. Class F 중폭기의 출력단 등가 회로

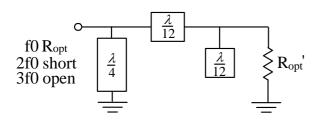

그림 3. 중폭기의 harmonic 제어를 위한 회로

과 전류 파형이 신호 주기 동안 overlap이 없는 것을 볼 수 있다. 따라서 이상적으로 전력 손실 없이 DC전력을 신호 전력으로 변환할 수 있게 된다. 그림 1의 출력 파형을 Fourier series로 분석해 보면수식 (1)과 수식(2)로 나타낼 수 있다.

$$I_d = i_{dpeak} \left(\frac{1}{\pi} + \frac{1}{2}\sin w_0 t - \frac{2}{\pi} \sum_{n=2.4.6}^{\infty} \frac{1}{n^2 - 1} \cos n w_0 t\right)$$

(1)

$$V_d = v_{dpeak} \left(\frac{1}{2} - \frac{2}{\pi} \sin w_0 t - \frac{2}{\pi} \sum_{n=3.5.7}^{\infty} \frac{1}{n} \sin n w_0 t\right)$$

(2)

수식에서 보듯이 전류 파형은 DC와 기본파, even harmonics로 구성되어 있고 전압 파형은 DC와 기본파, odd harmonics로 구성되어 있는 것을 알 수있다. Class F 증폭기는 출력 파형을 수식 (1), (2)와 같은 형태로 만들기 위해 그림 2와 같은 harmonic 제어 회로를 첨가하게 된다. 그림 2의 harmonic 제어 회로에서 network1과 network2는 even harmonics에 대해서 short되고 odd harmonics에 대해서 open으로 동작하게 된다. 한편 기본파에 대해서는 network1이 short되고 network2가 open이되기 때문에 결국 Ropt의 부하 임피던스를 보게 된다.

그러나 현실적으로 모든 harmonic을 제어하는 것이 불가능하므로 회로의 복잡성과 효율을 trade-off 해서 3차 harmonic까지 제어하는 형태가 일반적 이

다[3].

그림 3은 transmission line을 사용해 3차 harmonic까지 제어하는 회로를 보여주고 있다. 2차 harmonic에 대해  $\lambda/4$  short stub를 사용해 short을 잡고 3차 harmonic에 대해  $\lambda/12$  open stub와  $\lambda/12$  line을 사용해 open을 시킨다. 기본파에 대해서는 Ropt'의 부하 임피던스를 달아서 harmonic 제어 회로 앞에서 바라본 임피던스가 Ropt가 되게 한다.

## Ⅲ. 설계 및 시뮬레이션

설계에 사용된 simulator는 Agilent사의 ADS이며, 설계와 실험에 사용한 소자는 Motorola사의 10W급 LDMOS 소자인 MRF282를 사용하였다. MRF282는 2GHz에서 1-tone측정 시 9.5dB의 이득과 35%의 효율을 가지는 소자이다.

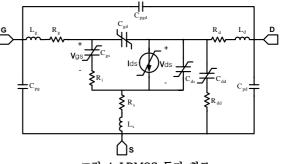

그림 4는 LDMOS의 등가회로를 나타낸 그림이다. 그림에서 보듯이 전류원 뒤로 선형 및 비선형 출력

그림 4. LDMOS 등가 회로

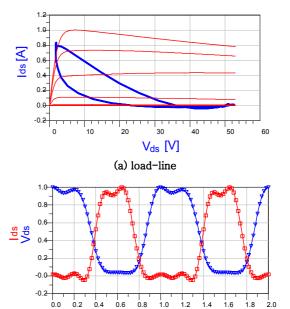

(b) I<sub>d</sub>, V<sub>d</sub> (normalized by peak value)

time, nsec

그림 5. 시간 영역에서 PTF10107 simulation 결과

capacitance를 포함한 package로 인한 기생 성분들이 있는 것을 알 수 있다. 이러한 기생 성분들을 보상하고 보다 효과적인 harmonic 제어를 위해  $\lambda/4$  short stub앞에 추가적인 line을 달고 harmonic 제어 회로를 최적화함으로써 전류원 바로 뒤에서 harmonic 제어가 이루어지도록 하였다. 또한 입력단에도 harmonic 제어 회로를 추가함으로써 입력전압 파형이 사각파와 유사한 신호가 인가되게 함으로써 증폭기의 효율 향상을 도모하였다[4].

이를 검증하기 위해 Ericsson사의 5W급 LDMOS 소자 PTF10107의 empirical model을 사용하여 simulation을 수행하였다[5].

그림 5는 PTF10107을 class F 증폭기로 설계하여 시간 영역에서 살펴본 simulation 결과이다. 그림 5(a)의 load-line과 그림 5(b)의 출력 파형에서 보듯이 설계된 증폭기가 class F로 적절하게 동작하는 것을 확인할 수 있다.

위에서 언급한 방식으로 MRF282 소자로 class F 증폭기를 설계해서 simulation했을 때 출력 전력 41.dBm에서 13.1dB의 이득과 81.2%의 drain efficiency 그리고 77.3%의 PAE를 기록했다.

그림 6. 제작된 증폭기의 실제 회로

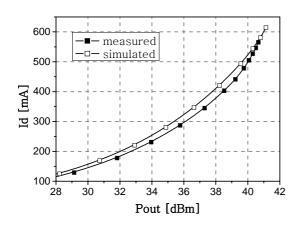

그림 7. Simulation과 측정에서의 DC 전류

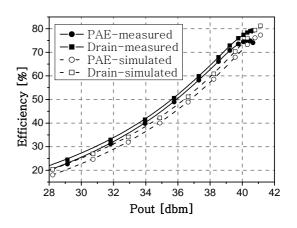

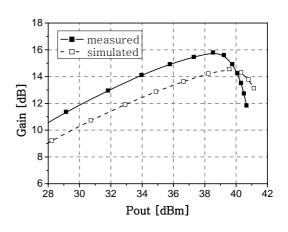

(a) Efficiency

(b) Gain 그림 8. Simulation과 측정에서의 Efficiency와 Gain

## Ⅳ. 제작 및 측정결과

그림 6은 simulation을 바탕으로 제작된 증폭기의 실제 모습이다. 증폭기의 성능을 최적화 하면서 class F 동작을 유지하기 위해 DC 전류 수준을 simulation과 비교하면서 matching 회로와 harmonic 제어 회로를 최적화 하였다.

설계된 class F 증폭기의 bias는 drain 전압 26V, gate 전압 2.1V이다. 그림 7은 simulation 했을 때의 DC 전류와 실제 제작된 증폭기의 DC 전류를 도시한 것이다. Saturation 되었을 때 simulation과 제작된 증폭기의 전류 수준이 비슷한 것을 볼 수 있다. 그림 8은 simulation과 측정에서의 효율과 이득을 나타낸 것이다. Single-tone 측정 결과 40.5dBm의 출력 전력에서 12.7dB의 이득과 drain efficiency 79%, PAE 74.8%의 높은 효율을 보였다. 제작된 증폭기가 simulation에서 나타난 것보다 saturation이다소 빠른 점을 제외하고는 simulation 결과와 측정결과가 거의 비슷한 성능을 나타냈다.

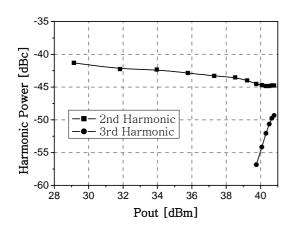

그림 9. 측정된 Harmonic Power

그림 9는 제작된 증폭기의 harmonic 전력을 도시한 것이다. 2차와 3차 harmonic 전력이 모두 - 40dBc 이하로 억제된 것을 볼 수 있다. 이는 2차 harmonic에 대해 short의 임피던스로 인해 전압이 0에 가깝기 때문이며 3차 harmonic에 대해서는 open의 임피던스를 보게 되어 전류가 0에 가깝기때문이다. 즉, harmonic 제어가 올바르게 되었다고판단할 수 있다.

## V. 결론

Transmission line을 사용하여 3차 harmonic까지 제어한 class F 형태의 증폭기를 설계하였다. 설계된 증폭기는 40.5dBm의 출력 전력에서 12.7dB의이득과 PAE 74.8%의 높은 효율을 보였다. 또한harmonic 전력이 모두 -40dBc이하로 억제되었다.

이는 class F 증폭기에서 가장 중요한 harmonic 제어가 소자의 전류원 바로 다음에서 이루어지게 함으로써 증폭기가 이상적인 class F 동작에 가깝게 했기 때문이다.

#### 참고 문헌

- [1] *Grebennikov, A. V.*, "Switched-mode tuned high-efficiency power amplifiers: historical aspect and future prospect", IEEE RFIC Symp., page 49-52, June 2002

- [2] *Grebennikov, A. V.*, "Circuit Design Technique for High Efficiency Class F Amplifier", IEEE MTT-S Int. Microwave Symp. *Dig.*, vol. 2, page 771-774, June 2000.

- [3] Raab, F. H., "Maximum efficiency and output of class-F power amplifiers", *IEEE Trans. MTT,* vol. 49, no. 6, page 1162-1166, June 2001.

- [4] Rudiakova, A.N., Krizhanovski, V.G., "Driving waveforms for class-F power amplifiers [GaAs MESFETs]", IEEE MTT-S Int. Microwave Symp. Dig., vol. 1, page 473-476, June 2000.

- [5] Youngoo Yang, Youngyun Woo, Jaehyok Yi, Bumman Kim, "A new empirical large-signal model of Si LDMOSFETs for high-power amplifier design", *IEEE Trans. MTT*, vol. 49, no. 9, page 1626–1633, Sept 2001.